Chips

Connecting Chips, Expanding Possibilities

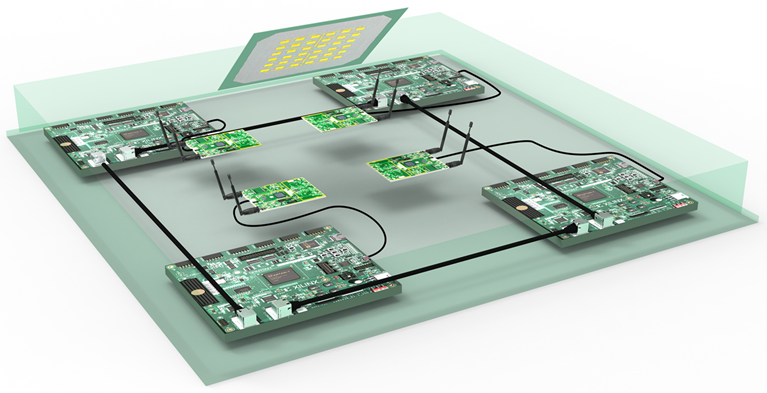

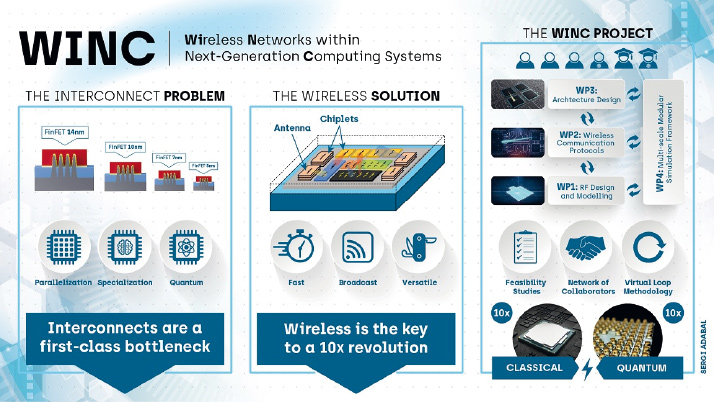

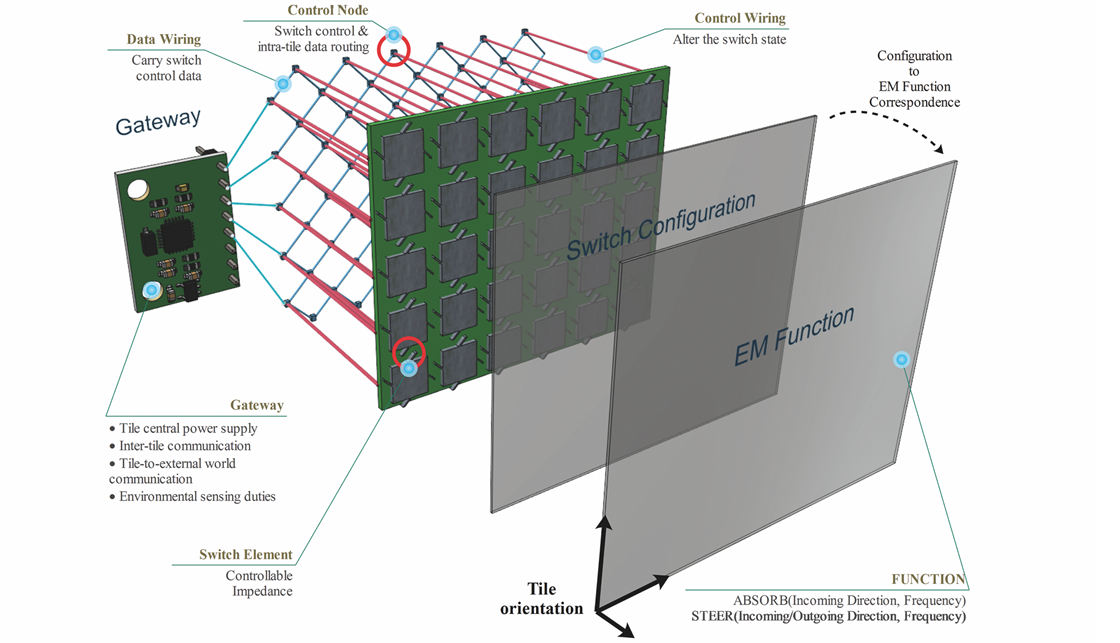

The CHIPS research group is dedicated to pioneering advancements in chip and package-scale communication infrastructures, which are essential for the next generation of computer architectures. We focus on three primary areas: general-purpose many-core systems, supercomputers, and deep neural network (DNN) accelerators. Each area presents unique challenges and opportunities for innovation in how data is exchanged and processed. For general-purpose many-core systems, we are developing scalable, high-throughput communication frameworks that enhance parallelism and efficiency. In the realm of supercomputers, our work aims to minimise latency and maximise bandwidth to handle increasingly complex simulations and computations. Our efforts in DNN accelerators focus on optimising dataflow between highly specialised processing units to significantly speed up artificial intelligence (AI) and machine learning (ML) tasks. At the heart of all these explorations lies a key enabling technology: wireless interconnects within chips and packages. Using this technology, we seek to reduce wiring complexity, enhance data transfer rates, and improve overall system flexibility. Through collaborative research and technological exploration, our group aims to set the foundation for the computational capabilities of tomorrow, ensuring that advancements in hardware keep pace with the ever-growing demands of software applications and computational theory.

Abhijit Das

Group Leader

As the leader of the Chips research group, Dr. Abhijit Das envisions forging new pathways in chip and package-scale communication infrastructures. He is passionate about pushing the limits of what is possible, fostering an environment where innovation thrives, and groundbreaking ideas are brought to fruition. He plans to steer the research towards harnessing the full potential of wireless interconnects within chips and packages, a technology he believes will be pivotal in revolutionising future computer architectures. Collaboration and interdisciplinary research are at the heart of his approach. He is committed to building strong partnerships with academic institutions and industry leaders to accelerate the translation of the group’s work into impact-worthy publications and real-world applications. Through this journey, Dr. Das aspires to position the Chips research group at the forefront of technological innovation, setting the stage for the computational breakthroughs of tomorrow.

PROJECTS

SELECTED PUBLICATIONS

Graphene-based Wireless Agile Interconnects for Massive Heterogeneous Multi-chip Processors

S. Abadal, R. Guirado, H. Taghvaee, A. Jain, E. Pereira de Santana, P. Haring Bolívar, M. Saeed, R. Negra, Z. Wang, K-T. Wang, M. C. Lemme, J. Klein, M. Zapater, A. Levisse, D. Atienza, D. Rossi, F. Conti, M. Dazzi, G. Karunaratne, I. Boybat and A. Sebastian