# Channel Characterization for Chip-scale Wireless Communications within Computing Packages

Xavier Timoneda\*, Albert Cabellos-Aparicio\*, Dionysios Manessis†, Eduard Alarcón\*, Sergi Abadal\*

\*NaNoNetworking Center in Catalunya (N3Cat), Universitat Politècnica de Catalunya (UPC), Barcelona, Spain

†Fraunhofer Institute for Reliability and Microintegration (IZM), Berlin, Germany

Email: xavier.timoneda@upc.edu, acabello@ac.upc.edu, dionysios.manessis@izm.fraunhofer.de,

eduard.alarcon@upc.edu, abadal@ac.upc.edu

Abstract—Wireless Network-on-Chip (WNoC) appears as a promising alternative to conventional interconnect fabrics for chip-scale communications. WNoC takes advantage of an overlaid network composed by a set of millimeter-wave antennas to reduce latency and increase throughput in the communication between cores. Similarly, wireless inter-chip communication has been also proposed to improve the information transfer between processors, memory, and accelerators in multi-chip settings. However, the wireless channel remains largely unknown in both scenarios, especially in the presence of realistic chip packages. This work addresses the issue by accurately modeling flip-chip packages and investigating the propagation both its interior and its surroundings. Through parametric studies, package configurations that minimize path loss are obtained and the trade-offs observed when applying such optimizations are discussed. Single-chip and multi-chip architectures are compared in terms of the path loss exponent, confirming that the amount of bulk silicon found in the pathway between transmitter and receiver is the main determinant of losses.

#### I. INTRODUCTION

Recent years have witnessed a rising interest towards heterogeneous multi-chip architectures and the so-called 2.5D integration. The reasons are various, but mostly have their origin in the diminishing returns of transistor scaling and the cost of manufacturing large chips. In this context, heterogeneous multi-chip architectures allow to increase *performance* of multicore processors beyond the limits of a large monolithic chip [1]; reduce their manufacturing *cost* by disintegrating a large monolithic chip into a network of smaller ones, but with much better yield [2]; and provide *versatility* or even *modularity* in response to the increasing appeal of co-integrating diverse components such as CPUs, GPUs, memories, or accelerators within a single package [3].

The new integration trends have strong consequences on the design of the communications backbone within the package. On the one hand, with the recent introduction of silicon interposers in 2.5D processes, there has been a reduction of the performance and cost difference between on-chip and off-chip communication [4]. Also, interposers may be capable of hosting *off-chip routers* in the future [2]. On the other

The authors gratefully acknowledge support from the Spanish MINECO under grants PCIN-2015-012 and under contract TEC2017-90034-C2-1-R (ALLIANCE project) that receives funding from FEDER, from the EU's H2020 FET-OPEN program under grant No. 736876 (VISORSURF), and by the Catalan Institution for Research and Advanced Studies (ICREA).

hand, increased system heterogeneity implies higher versatility requirements as the actual communication needs will depend on the actual constituents of the architecture.

It is expected that within-package networks will exploit the interposer advantages and rely on a tighter integration of the on-chip and off-chip sub-systems [2]. However, as off-chip transfers keep being expensive, it remains unknown whether such approach alone will suffice to meet the requirements of this scenario. As a result, emerging interconnect technologies are being explored as well [5], [6]. Among them, wireless chip-scale communications show great promise due to its inherent lack of path infrastructure. This allows to overcome pin limitations and contribute to versatility by providing low-latency broadcast capabilities across the package [7].

Research in highly-integrated wireless communications has exploded in the last decade [8]–[17]. The heterogeneous integration tendency has also impacted on this field, leading to several works of that explicitly consider wireless communications across chips for CPU-GPU coordination [18], integrated memory access [19], [20], or in a more generic intra-/inter-chip framework [21].

A missing piece in the wireless chip-scale puzzle is, however, the characterization of the wireless channel. The theory is well laid out [22] and a wide variety of works exist at on-chip [23]–[25], off-chip [26]–[28] and PCB board levels [29]–[31]. However, as detailed in Section V, very few studies include the chip package in their simulations or measurements and, those that do it, are limited to low frequencies or lack proper justifications on the antenna type and placement [32]–[34]. Note that, without proper understanding of the wireless channel within package, the path loss and dispersion assumptions may be overly optimistic. This affects the transceiver design and leads to inaccurate performance and efficiency reports. As most architectural studies rely in such figures, the impact of the wireless chip-scale paradigm cannot be really assessed.

This paper aims to address this issue by providing a characterization of wireless channels compatible with heterogeneous 2.5D packaging. We rigorously model the package in a variety of single-chip and multi-chip configurations and discuss the antenna placement. By means of full-EM simulation, we extract the field distribution and coupling between antennas and then derive path loss models. Through parametric studies, we obtain optimal package dimensions for path loss minimization

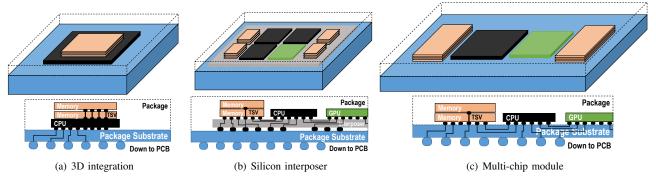

Fig. 1. Different heterogeneous integration techniques in examples with CPUs, GPUs, and memory. In a wireless approach, selected components would be equipped with one or several integrated antennas for wireless communication within the package.

and also analyze the impact of the die-package transitions in multi-chip configurations. Although the methodology is applicable to any antenna type and frequency range, we particularize it for the promising case of Through-Silicon Vias (TSVs) used as monopoles in the range of 50–150 GHz.

The remainder of the paper is as follows. Section II presents the system model, including details of the chip package and main assumptions. Section III describes the simulation methodology and subsequent channel modeling, whereas Section IV presents the main results. Finally, Section V analyzes related works and Section VI concludes the paper.

## II. SYSTEM MODEL

This work considers a variety of multi-chip configurations for the channel characterization, summarized in Figure 1. All cases assume flip-chip integration. Although heat dissipation schemes are generally applied on a per-chip basis, here we propose the addition of a single heat spreader common to all chips and then the heat sink on top. Next, we provide more details on the structure of the package, dimensions, and materials.

## A. Multi-chip Integration

The (heterogeneous) integration of multiple chips currently takes place either vertically or horizontally. The former, represented in Figure 1(a), consists on the stacking of several chips that have been previously thinned down below 100  $\mu$ m [35]. Once stacked, the chips are interconnected through a forest of vertical TSVs with very fine pitch. This provides a huge bandwidth density and efficiency due to the very short link lengths. On the downside, 3D integration suffers from evident heat dissipation issues and the available area of integration basically depends on the dimensions of the chip at the base, i.e. around  $20\times20~\text{mm}^2$ .

Contrary to 3D stacking, heterogeneous 2.5D integration takes a co-planar approach and interconnects chips either through a common platform [4]. Depending on the level of integration, this common platform may be silicon interposer (Fig. 1(b)) or the package substrate in a more classical Multi-Chip Module (MCM) approach (Fig. 1(c)). Such an arrangement alleviates the heat dissipation issue of 3D stacking

and also increases the available area, as the limit is now set by the interposer  $(24\times36~\text{mm}^2~\text{in}~[2],~40\times40~\text{mm}^2~\text{in}~[4])$  or the substrate  $(77\times77~\text{mm}^2~\text{in}~[1])$ . It also reduces the cost of the interconnects, as the pitch of TSVs is significantly coarsened. The main downturn of the approach is the reduction of bandwidth density and efficiency due to pin limitations and the need for longer links.

As for heat dissipation, it is worth noting that heat dissipation schemes are generally applied to each chip individually and then covered by a common lid. Instead, in his work we propose the addition of a single heat spreader common to all chips of a multi-chip configuration, and then a single heat sink on top. This would enhance heat dissipation further and favor inter-chip propagation through a common layer, reducing losses due to reflections at the chip-package interfaces. Molding compounds are sometimes used to fill the gaps between chips and below the heat spreader [36]. However, due to its poor thermal behavior, we advocate to the direct interfacing of the chip with the heat spreader. The lateral space between chips is assumed to be filled with air or vacuum.

This paper explicitly considers wireless communication in 2.5D environments. To this end, we model the interposer and MCM cases and comparing them with single-chip architectures. Therefore, the 3D stacking case is also indirectly represented: a single-chip architecture with thin silicon can be seen as a 3D stack as long as the antenna is placed on the top layer, just before the heat spreader.

## B. Flip-chip Package

Although a recent work suggests a packageless architecture [37], dies have historically included a package to (i) act as a space transformer for I/O pins, provide mechanical support to the dies, and (iii) for ease of testability and repairability. Some packages include a molding compound around the chip to improves mechanical stability [36], but its typically poor thermal conductivity discourages its use in hot architectures. In most cases, even the packageless one [37], the die can be contacted directly by a Thermal Interface Material (TIM) with a metallic heat sink on top, avoiding the use of the molding compound.

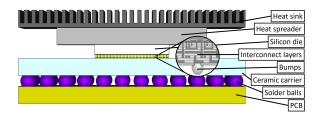

Fig. 2. Schematic of the layers of a flip-chip package

TABLE I

CHARACTERISTICS OF THE LAYERS IN A COMPUTING PACKAGE

|                  | Thickness | Material       | $\varepsilon_r$ | $tan(\delta)$ |

|------------------|-----------|----------------|-----------------|---------------|

| Heat sink        | 0.5 mm    | Aluminum       | -               | -             |

| Heat spreader    | 0.8 mm    | Thermal cond.  | 8.6             | $3.10^{-4}$   |

| Silicon die      | 0.2 mm    | Bulk Silicon   | 11.9            | 0.2517        |

| Interconnections | 13 μm     | Cu and $SiO_2$ | 3.9             | 0.03          |

| Bumps            | 87.5 μm   | Cu and Sn      | -               | -             |

| Interposer       | 0.1 mm    | Bulk Silicon   | 11.9            | 0.2517        |

| Ceramic carrier  | 0.5 mm    | Alumina        | 9.4             | $4.10^{-4}$   |

This work considers a flip-chip package with solder bumps. The packaging procedure is summarized here; we refer the reader to [38] and references therein for more details. During the manufacturing process, the solder bumps are deposited on the chip pads, which already carry a valid under bump metallization (UBM) like nickel/gold (Ni/Au). Then, the chip is flipped over and its solder bumps are aligned precisely to the pads of the package carrier external circuit. This is in contrast to wire bonding of chips on the package substrate or the interposer, in which the chip is mounted upright and wires are used to interconnect the chip pads to external circuitry [33]. Flip chip is generally preferred over wire bonding due to (i) its much lower inductance given by the shorter interconnect length [39], (ii) lower power-ground inductance due to direct routing of power, and (iii) higher power density given by the use of the whole chip surface.

An instance of the resulting complete package is shown in Figure 2. The layers are described from top to bottom as summarized in Table I. On top, the heat sink and heat spreader dissipate the heat out of the silicon chip, as they both have good thermal conductivity. Bulk silicon serves as the foundation of the transistors. This layer has low resistivity ( $10~\Omega$ -cm), which is convenient for the operation of transistors, but not for electromagnetic propagation [40]. The interconnect layers, which occupy the bottom of the silicon die as shown in the inset of Fig. 2, are generally made of copper and surrounded by an insulator such as silicon dioxide (SiO<sub>2</sub>) [41]. Depending on the case, we find a silicon interposer or a package substrate below the micro-bumps.

#### C. Package Optimization for EM Propagation

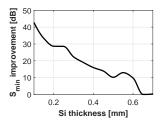

In our previous work, we discussed the impact of the different materials of a chip package on electromagnetic propagation. As pointed out above, the chip substrate and the heat spreader are the main determinants of the path loss and, by modifying their thicknesses, we can optimize propagation.

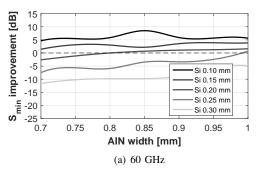

- (a) Improvement over 0.7-mm Si

- (b) Improvement over no AIN

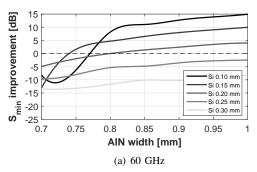

Fig. 3. Adjusting the Silicon and heat spreader thickness result in huge improvements in the path loss.

The bulk silicon used in the chip substrate generally has low resistivity, which means a high loss tangent, and therefore we proposed to thin it to minimize propagation at this layer. To quantify the gains of this process, in [38] we studied the path loss for different silicon thickness values in a single-chip package. We took 100 µm as lower limit, frequently assumed in 3D stacking, although chip makers can reportedly reduce that further to tens of microns [42]. As we can see in Fig. 3(a), the path loss difference between the 0.1-mm and 0.7-mm cases is over 40 dB. Henceforth, we take 200 µm as the value by default.

The materials used as heat spreaders have good thermal properties and, coincidentally, low electrical losses [40]. To study their potential impact on electromagnetic propagation, in [38] we simulated a chip package with different heat spreader thicknesses –our choice was Aluminum Nitride (AIN). As observed in Fig. 3(b), thickening the heat spreader reduces losses up to 33 dB with respect to not having any heat spreader. Therefore, it is a parameter to consider in package engineering efforts. Henceforth, we consider a 800 µm AIN layer as the heat spreader by default.

#### D. Antenna Integration

The antenna placement within a flip-chip package is another important design consideration. Placing the radiating element as far from the lossy silicon as possible, as proposed in several works [23], [43], [44], is not realistic because the antenna would be short-circuited by the array of micro-bumps. Instead, printed dipoles [33] or patch antennas [45] may be implemented in the metal layers closest to the silicon. However, the proximity of the antennas to the *virtual ground plane* formed by the array of micro-bumps reduces their efficiency, whereas co-planarity between antennas further increases losses.

Finally, one could use TSVs as quarter-wave monopole antennas for several reasons: (i) the antenna would radiate laterally, directly towards the receiving antennas; (ii) advanced TSV and electroplating techniques [46] would allow fine-tuning the antenna to the desired frequency; and (iii) the array of micro-bumps would naturally act as a ground plane, allowing to see the quarter-wave monopole effectively as a dipole. Note that vertical on-chip monopoles have been proposed recently [47], but using non-standard fabrication and packaging.

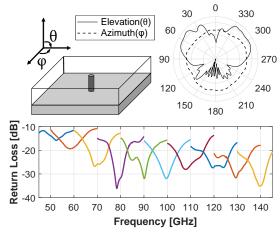

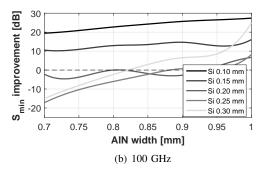

Fig. 4. Schematic representation of an on-chip monopole, expected radiation pattern, and return loss for instantiations optimized at 50–140 GHz.

Given the promising performance of monopoles in the chipscale environment, we will consider them throughout this work. Figure 4 shows a sketch together with the expected radiation pattern within the package.

## III. METHODOLOGY

The canonical structure of Fig. 2 is introduced in CST MWS [48] with the parameter values from Table I. We then modify the structure to model the different scenarios depicted in Fig. 1 and to perform package optimizations. To reduce the computational burden, we perform several approximations that do not affect the accuracy of the results. For instance, given their fine-grained pitched at mm-Wave frequencies, the micro-bump array placed between the chip and the package substrate/interposer is modeled as solid metallic element [38].

The monopole antenna is modeled as a thin and long cylindrical metallic structure, placed vertically passing through the silicon. Through optimization-driven simulations, the length of the monopole is adjusted to minimize the return loss at the central frequency of interest. By default, simulations are by default centered at 60 GHz with 20 GHz bandwidth. However, explorations at higher frequencies are also performed after the respective monopole length adjustments. Figure 4 shows the return loss of the different monopole instances.

Simulations consider a number of antennas evenly distributed across the chips. The outcomes are the field distribution, the antenna gain, and the coupling between antennas. Let  $\overline{S_{ij}}$  be the average of the coupling between transmitter j and receiver i over the whole frequency band. The minimum of  $\overline{S}$  is used as a benchmark to evaluate the worst case for several material thickness combinations. It can be expressed as:

$$S_{min} = \min_{i,j \neq i} \overline{S_{ij}}.$$

(1)

With the S-parameters, the channel frequency response  $H_{ij}(f)$  can be then evaluated for each antenna pair as

$$G_i G_j |H_{ij}(f)|^2 = \frac{|S_{ji}(f)|^2}{(1 - |S_{ii}(f)|^2) \cdot (1 - |S_{jj}(f)|^2)}, \quad (2)$$

where  $G_i$  and  $G_j$  are the transmitter and receiver antenna gains,  $S_{ji}$  is the coupling between transmitter i and receiver j, whereas  $S_{ii}$  and  $S_{jj}$  are the reflection coefficients at both ends [49]. Once evaluated, a path loss analysis can be performed by fitting the attenuation over distance to

$$L_{dB} = 10n \cdot \log_{10}(d) + C, (3)$$

where d is the distance between antennas and n is the path loss exponent [23]. The path loss exponent is around 2 in free space, below 2 in guided or enclosed structures, and above 2 in lossy environments.

#### IV. SIMULATION RESULTS

In the following, we show the results of an extensive simulation study that explores the channel characteristics in single-chip and multi-chip settings. We perform package optimizations to minimize path loss and assess the impact of having a multiple chips on the optimal design point. Additionally, we explore the scaling with frequency.

## A. On-chip wireless channel in single-chip package

We start by exploring the channel within a single-chip package. This models conventional processors, but also serves for 3D stacking if we assume that antennas are placed at the top chip –the one interfaced by the heat spreader. For this scenario, we consider a single square chip 22-mm long and wide, surrounded by conducting walls representing the package boundaries. The conducting walls are placed 5 mm away of the chip limits. The space between the chip and the walls is modeled as vacuum, although it could be filled with molding compound as discussed in Section II.

Package Optimization at 60 GHz. As indicated in Section II-C, it is preferable to keep the silicon thickness to a minimum and to increase that of the heat spreader. When introducing the antenna, results may oscillate and an antenna-package co-design may be required for optimization. Fig. 5(a) shows the results of such co-design, which keeping the monopole matched at 60 GHz at all times. It is found that the optimal silicon and AIN thicknesses are 0.10 mm and 0.85 mm, respectively, as they yield the highest mean of the worst case coupling. This shows that fine-grained optimization can provide extra 5–10 dB of path loss reduction.

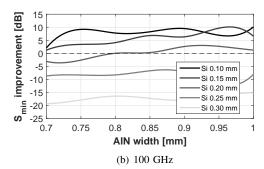

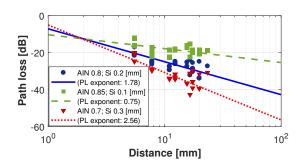

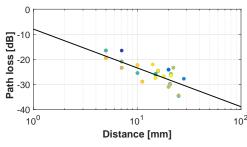

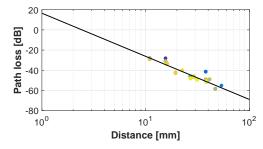

Path loss at 60 GHz. To further highlight the importance of package optimization, we performed a path loss analysis at 60 GHz. We considered three different cases: default dimensions as specified in Table I, optimal dimensions as obtained in Fig. 5(a), and a quite suboptimal design point. Remind that the path loss decouples the antenna effects and leaves just losses due to propagation. The results, plotted in Figure 6, shows how optimization reduces not only the path loss overall, but also the path loss exponent. For the default case, the path loss exponent is 1.78, slightly lower than the free space path loss, thanks to having a confined environment. In the optimal case, we are able to cut the exponent down to 0.75, thereby showing a strong waveguiding effect in propagation. The suboptimal

Fig. 5. Improvement of worst-case coupling  $S_{min}$  in the single-chip case at two frequency points. The baseline dimensions are specified in Table I.

Fig. 6. Path loss as a function of distance, including linear regression fitting, for the single-chip case at 60 GHz.

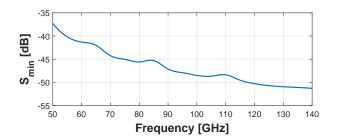

Fig. 7. Worst-case coupling  $S_{min}$  as a function of frequency in the single-chip case with the thicknesses specified in Table I.

case, with an exponent higher than 2, demonstrates that the losses introduced by silicon cannot be neglected.

**Frequency sweep.** Increasing the frequency of operation leads to smaller antennas and, potentially, smaller transceivers. Also, the absolute bandwidth is generally improved. Therefore, it is of great interest to study the scaling trends of the onchip channel. Figure 7 shows how  $S_{min}$  scales over frequency. This sweep was performed with the default silicon and heat spreader widths, 0.2 mm and 0.8 mm, respectively. We can observe that in overall, the loss between links increases with frequency probably due to two reasons: the antennas have smaller apertures, and the propagation losses at the dielectrics are larger. Nevertheless, this effect is compensated in part by the enclosed nature of the on-chip scenario, mitigating the impacts of frequency scaling.

Impact of frequency on package optimization. Since our

methodology performs a joint antenna-package optimization, it is reasonable to think that the optimal point will change with frequency. To illustrate this, we performed the exploration with the monopole tuned at 100 GHz. Figure 5(b) shows how the optimal point has slightly changed, but the tendency of higher losses with a thicker silicon is indeed, increased. This can be explained by the fact that losses on the silicon are frequency sensitive. Still, the improvement with respect to the default case is 10 dB and can be achieved even with 0.15mm of silicon.

## B. On-chip wireless channel in multi-chip package

Let us now consider a single chip isolated in a package without lateral walls. This would *a priori* model the worst case for on-chip propagation in a multi-chip package, where lateral walls are far away and neighboring chips absorb most of the incoming energy. Indeed, the absence of reflecting elements nearby is expected to lead to a reduction of the energy that returns to the chip after leaving, therefore increasing the path loss. To evaluate this scenario, we consider a 22×22 mm<sup>2</sup> chip whose boundaries model a perfect matching layer (PML), giving the impression of an infinitely wide package without walls.

Impact of boundaries on loss between links. Without lateral walls, the loss of the worst-case link is increased up to 27 dB higher for the thicknesses of Table I (from -43 dB to -70 dB). This is due to the harsh reduction of the power received by the antenna at the opposite corner of the radiating one, as the majority of the power to this antenna was coming from the now non-existent reflections at the package walls. This results strongly suggests that, being either due to losses or security reasons (so that wireless signals cannot escape outside the package), having package walls is beneficial.

Impact of boundaries on package optimization. As we can see on Figures 8(a) and 8(b), the variation of  $S_{min}$  with respect to non-optimized case is large and more sensitive to the silicon thickness. Due to the absence of walls, package optimization plays an even more important role than with walls (Fig. 5). The improvement is larger than 20 dB in several cases. Note, also, that the exploration also unveiled very detrimental  $S_{min}$  dips at certain thickness combinations. See, for instance, the 0.1-mm silicon and 0.7-mm AIN case at 60 GHz in Figure 8(a).

Fig. 8. Improvement of worst-case coupling  $S_{min}$  in the multi-chip case (without lateral walls) at two frequency points. The baseline dimensions are specified in Table I.

## C. Off-chip wireless channel in multi-chip package

We finally consider a full multi-chip packages as represented in Figures 1(b) and 1(c). In the interposer case, we evaluate an array of  $2\times2$  small chips, 10 mm in length each, placed inside a  $33\times33$  mm<sup>2</sup> package with a separation of 5 mm between chips. The silicon interposer has 0.1 mm of thickness and 33 mm of length and width. In the MCM case, we simulate  $2\times2$  chips of standard size, placed inside a bigger package whose length and width is 59 mm.

We place four antennas per chip, regardless of the chip size, in order to evaluate all the possible combinations, i.e., close or distant antennas in close or distant chips. All the multichip package simulations are performed with enclosing conducting walls and a common heat spreader for all chips.

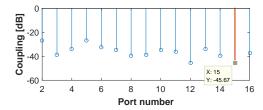

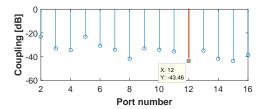

Small chips vs single standard chip. The silicon interposer case allows us to evaluate the impact of processor disintegration [2] on the wireless channel characteristics. To this end, we compare the coupling between antennas in a single large chip, Fig. 9(a), and multiple small chips, Fig. 9(b). The plots do not illustrate large changes overall —a slightly better coupling is observed in the interposer case (only a few dBs in most antenna pairs, including  $S_{min}$ ). There are two effects that seem to be canceling out: on the one hand, propagation occurring in the vacuum space between chips instead of in lossy silicon would lead to better coupling in the interposer case. On the other hand, reflections due to media changes (silicon–vacuum–silicon) are also higher in the interposer case, which may be leading to lower coupling in far away antennas. This may also explain the better coupling at nearby antennas (port 2 and 5).

Path loss: interposer vs MCM. The path loss exponent is calculated for the two multi-chip scenarios and compared with that of 3D stacking, previously shown in Fig. 6. In all cases, we considered the default thicknesses specified in Table I. The path loss exponent of the interposer scenario, plotted in Figure 10(a), is 1.55. This is slightly lower than the exponent of the single-chip case (1.78), thanks to the lack of silicon between chips. The path loss exponent increases up to 4.27 for MCM case, plotted in Fig. 10(b), due to the crescent losses due to propagation through lossy silicon as the distance between antennas increases. This confirms that the amount of silicon that waves need to traverse is the main determinant of losses.

#### V. RELATED WORK

Channels within a Chip Package: the existence of a wireless channel in flip-chip packages was suggested in [32] and then experimentally validated at 15 GHz in [33]. Recently, the work by Narde *et al.* analyzes the S-parameters for one and two chips within the same package assuming planar zigzag antennas at 60 GHz [34]. Although becoming part of the radiative structure by capacitive coupling, the effect of bumps on the antenna response is not discussed. They also assume high-resistivity silicon, which may be unlikely in processor dies. Our previous works, instead, discuss different 60-GHz antenna types and perform field distribution and path loss analysis within a single-chip package with bulk silicon [38], [50]. The present work extends the frequency range up to 150 GHz and considers multiple single-chip and multi-chip configurations, both MCM and interposer-based.

Channels within a Metallic Casing: Matolak *et al.* suggested that the wireless chip-scale communications would act as a micro-reverberation chamber with metallic walls [22], although they did not discuss the package. Others have explored a similar scenario over a large PCB board, including DRAM modules and other components within a computer case up to 300 GHz [26], [29]–[31]. In [51], the authors explored waveguide-like millimeter-wave channels within a reconfigurable metamaterial that integrates multiple chips on a PCB. Finally, the 60-GHz channel has been also studied in larger enclosed environments such as printers [52] or data center cabinets [53], which also act as reverberation chambers. Although these structures may capture the enclosed nature of a chip package, they have substantially different dimensions, materials, and antenna placement restrictions.

Chip-scale Channels without Package: studies of the onchip and off-chip wireless channels have been often conducted without considering any particular package, assuming free space over the insulator layer. Yan *et al.* provided a theoretical basis at millimeter-wave frequencies [54], whereas others provided simulation-based studies [27], [55], [56] or actual measurements using planar antennas [23], [57] and bondwire antennas [8]. In the terahertz band analysis of [25], the package structure is described, but then neglected for simplicity. Finally, monopoles placed in a loosely defined

- (a) Single standard chip on package substrate.

- (b) Four small chips on silicon interposer.

Fig. 9. Mean of the S-parameter for each antenna pair assuming transmission from port 1 at 60 GHz.  $S_{min}$  is highlighted.

- (a) Four small chips on silicon interposer.

- (b) Four standard chips on MCM package.

Fig. 10. Path loss as a function of distance, including linear regression fitting, for the multi-chip cases at 60 GHz.

superstrate have been also studied in recent works [24], [47]. All these works, however, do not provide a faithful view of a chip package and cannot be re-used for the scenario at hand.

#### VI. CONCLUSION

The characterization of the wireless channel in scenarios compatible with standard chip packages is largely missing in the literature. To start bridging this gap, here we have performed a frequency-domain analysis of mm-wave propagation in the 3D stacking, silicon interposer, and multi-chip module schemes. We highlight the importance of package optimization to ensure the feasibility of the WNoC approach, as it is capable of reducing path losses by several tens of dBs. We also conclude that such optimization is dependent on the frequency of operation and the elements surrounding the chips. Finally, a path loss analysis confirms that propagation length within silicon is the main determinant of losses, and that finding the right package dimensions ensure the scalability of the approach.

#### REFERENCES

- [1] A. Arunkumar, E. Bolotin, B. Cho, U. Milic, E. Ebrahimi, O. Villa, A. Jaleel, C.-J. Wu, and D. Nellans, "MCM-GPU: Multi-Chip-Module GPUs for Continued Performance Scalability," *Proceedings of the ISCA* '17, pp. 320–332, 2017.

- [2] A. Kannan, N. Enright Jerger, and G. H. Loh, "Exploiting Interposer Technologies to Disintegrate and Reintegrate Multicore Processors," *IEEE Micro*, vol. 36, no. 3, pp. 84–93, 2016.

- [3] J. Yin, Z. Lin, O. Kayiran, M. Poremba, M. S. Bin Altaf, N. Enright Jerger, and G. H. Loh, "Modular Routing Design for Chiplet-based Systems," *Proceedings of the ISCA '18*, 2018.

- [4] X. Zhang, J. K. Lin, S. Wickramanayaka, S. Zhang, R. Weerasekera, R. Dutta, K. F. Chang, K. J. Chui, H. Y. Li, D. S. Wee Ho, L. Ding, G. Katti, S. Bhattacharya, and D. L. Kwong, "Heterogeneous 2.5D integration on through silicon interposer," *Applied Physics Reviews*, vol. 2, no. 2, 2015.

- [5] J. Kim, K. Choi, and G. Loh, "Exploiting new interconnect technologies in on-chip communication," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 2, no. 2, pp. 124–136, 2012.

- [6] C. Thraskias, E. Lallas, N. Neumann, L. Schares, B. Offrein, R. Henker, D. Plettemeier, F. Ellinger, J. Leuthold, and I. Tomkos, "Survey of Photonic and Plasmonic Interconnect Technologies for Intra-Datacenter and High-Performance Computing Communications," *IEEE Communi*cations Surveys and Tutorials, 2018.

- [7] S. Deb, A. Ganguly, P. P. Pande, B. Belzer, and D. Heo, "Wireless NoC as Interconnection Backbone for Multicore Chips: Promises and Challenges," *IEEE Journal on Emerging and Selected Topics in Circuits and Systems*, vol. 2, no. 2, pp. 228–239, 2012.

- [8] W.-H. Chen, S. Joo, S. Sayilir, R. Willmot, T.-Y. Choi, D. Kim, J. Lu, D. Peroulis, and B. Jung, "A 6-Gb/s Wireless Inter-Chip Data Link Using 43-GHz Transceivers and Bond-Wire Antennas," *IEEE Journal of Solid-State Circuits*, vol. 44, no. 10, pp. 2711–2721, oct 2009.

- [9] G. P. Fettweis, N. ul Hassan, L. Landau, and E. Fischer, "Wireless Interconnect for Board and Chip Level," in *Proceedings of the DATE* '13. New Jersey: IEEE Conference Publications, 2013, pp. 958–963.

- [10] P. Baniya, S. Yoo, K. L. Melde, A. Bisognin, and C. Luxey, "Switched-Beam 60-GHz Four-Element Array for Multichip Multicore System," IEEE Transactions on Components, Packaging and Manufacturing Technology, vol. 8, no. 2, pp. 251–260, 2018.

- [11] X. Yu, J. Baylon, P. Wettin, D. Heo, P. Pratim Pande, and S. Mirabbasi, "Architecture and Design of Multi-Channel Millimeter-Wave Wireless Network-on-Chip," *IEEE Design & Test*, vol. 31, no. 6, pp. 19–28, 2014.

- [12] M. Palesi, M. Collotta, A. Mineo, and V. Catania, "An Efficient Radio Access Control Mechanism for Wireless Network-On-Chip Architectures," *Journal of Low Power Electronics and Applications*, vol. 5, no. 2, pp. 38–56, 2015.

- [13] S. Abadal, A. Mestres, J. Torrellas, E. Alarcón, and A. Cabellos-Aparicio, "Medium Access Control in Wireless Network-on-Chip: A Context Analysis," *IEEE Communications Magazine*, vol. 56, no. 6, pp. 172–178, 2018.

- [14] D. DiTomaso, A. Kodi, D. Matolak, S. Kaya, S. Laha, and W. Rayess, "A-WiNoC: Adaptive Wireless Network-on-Chip Architecture for Chip Multiprocessors," *IEEE Transactions on Parallel and Distributed Sys*tems, vol. 26, no. 12, pp. 3289–3302, 2015.

- [15] S. Abadal, J. Torrellas, E. Alarcón, and A. Cabellos-Aparicio, "OrthoNoC: A Broadcast-Oriented Dual-Plane Wireless Network-on-Chip Architecture," *IEEE Transactions on Parallel and Distributed Systems*, vol. 29, no. 3, pp. 628–641, 2018.

- [16] S. Abadal, E. Alarcón, A. Cabellos-Aparicio, and J. Torrellas, "WiSync: An Architecture for Fast Synchronization through On-Chip Wireless Communication," in *Proceedings of the ASPLOS '16*, 2016, pp. 3–17.

- [17] W. Choi, K. Duraisamy, R. G. Kim, J. R. Doppa, P. P. Pande, D. Marculescu, and R. Marculescu, "On-Chip Communication Network for Efficient Training of Deep Convolutional Networks on Heterogeneous Manycore Systems," *IEEE Transactions on Computers*, vol. 67, no. 5, pp. 672–686, 2018.

- [18] S. H. Gade and S. Deb, "HyWin: Hybrid wireless NoC with sandboxed sub-networks for CPU/GPU architectures," *IEEE Transactions on Com*puters, vol. 66, no. 7, pp. 1145–1158, 2017.

- [19] M. A. I. Sikder, A. Kodi, W. Rayess, D. Ditomaso, D. Matolak, and S. Kaya, "Exploring wireless technology for off-chip memory access," in *Proceedings of the HOTI '16*, 2016, pp. 92–99.

- [20] Z. Liu, Y. Liang, N. Li, G. Feng, H. Yu, and S. Chen, "An Energy-efficient Adaptive Sub-THz Wireless Interconnect with MIMO-Beamforming between Cores and DRAMs," in *Proceedings of the* NANOCOM '16, 2016, pp. 1–6.

- [21] S. Shamim, N. Mansoor, R. S. Narde, V. Kothandapani, A. Ganguly, and J. Venkataraman, "A Wireless Interconnection Framework for Seamless Inter and Intra-chip Communication in Multichip Systems," *IEEE Transactions on Computers*, vol. 66, no. 3, pp. 389–402, 2017.

- [22] D. Matolak, S. Kaya, and A. Kodi, "Channel modeling for wireless networks-on-chips," *IEEE Communications Magazine*, vol. 51, no. 6, pp. 180–186, 2013.

- [23] Y. P. Zhang, Z. M. Chen, and M. Sun, "Propagation Mechanisms of Radio Waves Over Intra-Chip Channels With Integrated Antennas: Frequency-Domain Measurements and Time-Domain Analysis," *IEEE Transactions on Antennas and Propagation*, vol. 55, no. 10, pp. 2900–2906, 2007.

- [24] W. Rayess, D. W. Matolak, S. Kaya, and A. K. Kodi, "Antennas and Channel Characteristics for Wireless Networks on Chips," *Wireless Personal Communications*, vol. 95, no. 4, pp. 5039–5056, 2017.

- [25] Y. Chen and C. Han, "Channel Modeling and Analysis for Wireless Networks-on-Chip Communications in the Millimeter Wave and Terahertz Bands," in *Proceedings of the INFOCOM WKSHPS '18*, 2018.

- [26] Z. Chen and Y. Zhang, "Inter-chip wireless communication channel: Measurement, characterization, and modeling," *IEEE Transactions on Antennas and Propagation*, vol. 55, no. 3, pp. 978–986, 2007.

- [27] R. S. Narde and J. Venkataraman, "Feasibility study of Transmission between Wireless Interconnects in Multichip Multicore systems," in Proceedings of the APS/URSI '17, 2017, pp. 1821–1822.

- [28] P. Baniya, A. Bisognin, K. L. Melde, and C. Luxey, "Chip-to-Chip Switched Beam 60 GHz Circular Patch Planar Antenna Array and Pattern Considerations," *IEEE Transactions on Antennas and Propagation*, vol. 66, no. 4, pp. 1776–1787, 2018.

- [29] P. Y. Chiang, S. Woracheewan, C. Hu, L. Guo, H. Liu, R. Khanna, and J. Nejedlo, "Short-Range, Wireless Interconnect within a Computing Chassis: Design Challenges," *IEEE Design & Test of Computers*, vol. 27, no. 4, pp. 32–43, 2010.

- [30] H.-t. Wu, J.-j. Lin, and K. K. O, "Inter-Chip Wireless Communication," in *Proceedings of the EuCAP '13*, 2013, pp. 3647–3649.

- [31] S. Kim and A. Zajic, "Characterization of 300 GHz Wireless Channel on a Computer Motherboard," *IEEE Transactions on Antennas and Propagation*, vol. 64, no. 12, pp. 5411–5423, 2016.

- [32] K. Kim, W. Bornstad, and K. K. O, "A Plane Wave Model Approach to Understanding Propagation in an Intra-chip Communication System," in *Proceedings of the APS '01*, 2001, pp. 166–169.

- [33] J. Branch, X. Guo, L. Gao, A. Sugavanam, J. J. Lin, and K. K. O, "Wireless communication in a flip-chip package using integrated antennas on silicon substrates," *IEEE Electron Device Letters*, vol. 26, no. 2, pp. 115–117, 2005.

- [34] R. S. Narde, N. Mansoor, A. Ganguly, and J. Venkataraman, "On-Chip Antennas for Inter-Chip Wireless Interconnections: Challenges and Opportunities," in *Proceedings of the EuCAP '18*, 2018.

- [35] A. W. Topol, D. C. La Tulipe, L. Shi, D. J. Frank, K. Bernstein, S. E. Steen, A. Kumar, G. U. Singco, A. M. Young, K. W. Guarini, and M. Ieong, "Three-dimensional integrated circuits," *IBM Journal of Research and Development*, vol. 50, no. 4, pp. 491–506, 2006.

- [36] H. Ardebili and M. Pecht, Encapsulation technologies for electronic applications. William Andrew, 2009.

- [37] S. Pal, D. Petrisko, A. A. Bajwa, P. Gupta, S. S. Iyer, and R. Kumar, "A Case for Packageless Processors," in *Proceedings of the HPCA-24*, 2018, pp. 466–479.

- [38] X. Timoneda, S. Abadal, A. Cabellos-Aparicio, D. Manessis, J. Zhou, A. Franques, J. Torrellas, and E. Alarcón, "Millimeter-Wave Propagation within a Computer Chip Package," in *Proceedings of the ISCAS '18*, 2018.

- [39] S. L. Wright, R. Polastre, H. Gan, L. P. Buchwalter, R. Horton, P. S. Andry, E. Sprogis, C. Patel, C. Tsang, J. Knickerbocker, J. R. Lloyd, A. Sharma, and M. S. Sri-Jayantha, "Characterization of micro-bump C4 interconnects for Si-carrier SOP applications," in *Proceedings of the ECTC '06*, 2006, pp. 633–640.

- [40] K. Kimoto, N. Sasaki, S. Kubota, W. Moriyama, and T. Kikkawa, "High-Gain On-Chip Antennas for LSI Intra- / Inter-Chip Wireless Interconnection," *Proceedings of the EuCAP '09*, pp. 278–282, 2009.

- [41] O. Markish, B. Sheinman, O. Katz, D. Corcos, and D. Elad, "On-chip mmWave Antennas and Transceivers," in *Proceedings of the NoCS '15*, 2015, p. Art. 11.

- [42] F. Bieck, S. Spiller, F. Molina, M. Töpper, C. Lopper, I. Kuna, T. C. Seng, and T. Tabuchi, "Carrierless design for handling and processing of ultrathin wafers," *Proceedings of the ECTC '10*, pp. 316–322, 2010.

- [43] Y. P. Zhang, M. Sun, and L. H. Guo, "On-chip antennas for 60-GHz radios in silicon technology," *IEEE Transactions on Electron Devices*, vol. 52, no. 7, pp. 1664–1668, 2005.

- [44] F. Gutierrez, S. Agarwal, K. Parrish, and T. S. Rappaport, "On-chip integrated antenna structures in CMOS for 60 GHz WPAN systems," *IEEE Journal on Selected Areas in Communications*, vol. 27, no. 8, pp. 1367–1378, 2009.

- [45] H. Yordanov, V. Poulkov, and P. Russer, "On-Chip Monolithic Integrated Antennas Using CMOS Ground Supply Planes," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 6, no. 8, pp. 1268–1275, 2016.

- [46] Fraunhofer Institute for Reliability and Microintegration IZM, "All Silicon System Integration Dresden ASSID Fraunhofer IZM." [Online]. Available: https://www.izm.fraunhofer.de/en/abteilungen/\/high{\_}density{\_}interconnectwaferlevelpackaging/ausstattung/\/all{\_}silicon{\_}systemintegrationdresdenassid.html

- [47] J. Wu, A. Kodi, S. Kaya, A. Louri, and H. Xin, "Monopoles Loaded with 3-D-Printed Dielectrics for Future Wireless Intra-Chip Communications," *IEEE Transactions on Antennas and Propagation*, vol. 65, no. 12, pp. 6838–6846, 2017.

- [48] "CST Microwave Studio." [Online]. Available: http://www.cst.com

- [49] J. Lin, H. Wu, Y. Su, L. Gao, A. Sugavanam, and J. Brewer, "Communication using antennas fabricated in silicon integrated circuits," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 8, pp. 1678–1687, 2007.

- [50] X. Timoneda, S. Abadal, A. Cabellos-Aparicio, and E. Alarcón, "Modeling the EM Field Distribution within a Computer Chip Package," in *Proceedings of the WCNC '18*, 2018.

- [51] A. C. Tasolamprou, M. S. Mirmoosa, O. Tsilipakos, A. Pitilakis, F. Liu, S. Abadal, A. Cabellos-Aparicio, E. Alarcón, C. Liaskos, N. V. Kantartzis, S. Tretyakov, M. Kafesaki, E. N. Economou, and C. M. Soukoulis, "Intercell wireless communication in software-defined metasurfaces," in *Proceedings of the ISCAS '18*, 2018.

- [52] M. Ohira, T. Umaba, S. Kitazawa, H. Ban, and M. Ueba, "Experimental characterization of microwave radio propagation in ICT equipment for wireless harness communications," *IEEE Transactions on Antennas and Propagation*, vol. 59, no. 12, pp. 4757–4765, 2011.

- [53] S. Khademi, S. Prabhakar Chepuri, Z. Irahhauten, G. Janssen, and A.-J. van der Veen, "Channel Measurements and Modeling for a 60 GHz Wireless Link Within a Metal Cabinet," *IEEE Transactions on Wireless Communications*, vol. 14, no. 9, pp. 5098–5110, 2015.

- [54] L. Yan and G. W. Hanson, "Wave propagation mechanisms for intra-chip communications," *IEEE Transactions on Antennas and Propagation*, vol. 57, no. 9, pp. 2715–2724, 2009.

- [55] Y. Liu, V. Pano, D. Patron, K. Dandekar, and B. Taskin, "Innovative propagation mechanism for inter-chip and intra-chip communication," in *Proceedings of the WAMICON '15*, 2015.

- [56] S. H. Gade, S. Garg, and S. Deb, "OFDM Based High Data Rate, Fading Resilient Transceiver for Wireless Networks-on-Chip," in *Proceedings* of the ISVLSI '17, 2017, pp. 483–488.

- [57] H. H. Yeh, N. Hiramatsu, and K. L. Melde, "The design of broadband 60 GHz AMC antenna in multi-chip RF data transmission," *IEEE Transactions on Antennas and Propagation*, vol. 61, no. 4, pp. 1623–1630, 2013.